There have been a few changes behind the scenes but I hope you like the new look and that you can still find your way around the Forum!

There have been a few changes behind the scenes but I hope you like the new look and that you can still find your way around the Forum!

It’s IEDM week and from my position on the other side of the Pond (i.e. I’m not at the conference), it’s clear that interest in ReRAM and CBRAM continues. (As an aside, ReRAM seems to be losing the acronym battle with RRAM for resistive memory. I try not to use RRAM as it has been long used in another memory context where the first R stands for redundant…). However, this year there are more papers focussing on the access device suitable for use in next generation memory. This actually makes a lot of sense because:

-

a) Existing access (select) devices are usually far larger than the ~4F2 memory element, be it ReRAM, CBRAM or PCRAM. The obvious example is a 1T1R architecture where the T (transistor) is much larger than the R. I believe the smallest T’s in volume production are those used in DRAM where they approach 6F2. To support the programming currents in ReRAM/CBRAM one needs a transistor with larger footprint.

b) The access device requires a completely different characteristic to existing devices. For example, an ‘ideal’ device should have a <4F2 footprint which essentially means there is only room for two terminals and behave like a transistor, i.e. negligible voltage drop when on and negligible current leakage when off. A transistor achieves this by means of the third (gate) electrode.

c) The implementation of the architecture most often proposed for next generation resistive memory, the crossbar array, requires such a device to maximise array efficiency, i.e. mini$e co$t.

Crossbar have adopted a very high profile recently and their IEDM paper is focussed on their patented “field assisted superlinear threshold (select) device” which has an “ability to be integrated directly into each RRAM memory cell”. Certainly the details released are impressive such as “achieving the highest reported selectivity of 1010, as well as an extremely sharp turn-on slope of less than 5mV/dec, fast turn-on and recovery (<50ns), an endurance greater than 100M cycles, and a processing temperature less than 300°C” However, I was struck by the endurance number. While 10 8 is impressive, this precludes (direct) DRAM replacement and would ideally be much (much) greater than the endurance of the memory cell itself.

In terms of productization, Crossbar now say they have achieved “basic physics understanding and cell characterization, repeatability proven on small arrays using a prototype, (and) foundry transfer” leaving them one last step from commercialization, namely “volume manufacturing”. Given HP’s problems with this last step, let’s hope Crossbar are better prepared!

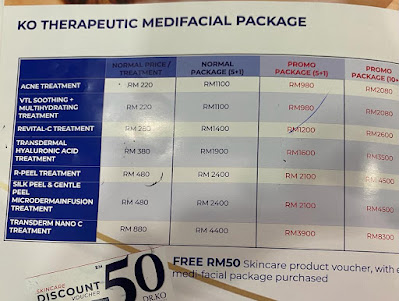

The four access devices compared, from IBM IEDM paper

The description of the Crossbar device reminded me of IBM’s MIEC device see Forum post. And indeed there is an update from the IBM group at IEDM on this device. . This paper compares the MIEC access device to three other types that have been described in the literature. (Always a brave thing to do, compare your breakthrough with other approaches to the same problem, Chapeau!). Basically all four can be thought of as back to back diodes where a reversible breakdown eliminates the drop across the reverse biased diode when the device is on. The paper goes on to describe the applicability of each access device in terms of the performance of the actual memory cell.

Interestingly, IBM see their MIEC device as being the best solution for a memory cell with a switching voltage around 1V and switching current >10uA as it would allow arrays >1Mb. With lower switching currents, the other approaches are also viable. Problems are foreseen with memory cells that require higher switching voltages at the high switching current as none of the devices appear to be viable for even small arrays…..

One thing that has puzzled me about the MIEC device is how fast it recovers from its ‘on’ state. When a voltage is applied, one can imagine that various mechanisms driven by ionic diffusion under the considerable electric field across the device could cause a large change in conductivity. However, once the field is removed, other slower diffusion processes are all that are available to restore the device to its initial (off) state. Thus I would expect a recovery period to be necessary. It appears I am mostly wrong but more on this in a future post!

Christie Marrian, ReRAM Forum Moderator